之前翻译的TSMC 5nm工艺总结 是Dick James发布在Semiconductor Digest上对台积电5nm制程的相关信息总结。从透露出来的信息来看,台积电将代替Intel,引领半导体制造行业的技术走向。James所提到的那个IEDM文档内,其实图片都是屏幕截图下来的(如下图所示),这篇文档还有其他信息没有展示出来。

所以接下来,我将结合之前所披露的5nm信息和这篇文档内的图表(包括被隐藏的),对台积电5nm工艺进行一个简短的解读,欢迎批评指正。

为了了解其5nm制程的一些细节,我们先回顾一下之前Scotten Jones对台积电5nm的分析: 台积电和三星的5nm工艺比较(下图)。在CPP 50nm,MP 30nm,SDB的情况下逻辑密度提升到了7nm的1.79倍,但是这次他们提供的是更激进的1.84倍(如下图所示),所以工艺上有更多的微缩和改进。

下面是对那篇文档内所有图表的解读。

下面是对那篇文档内所有图表的解读。

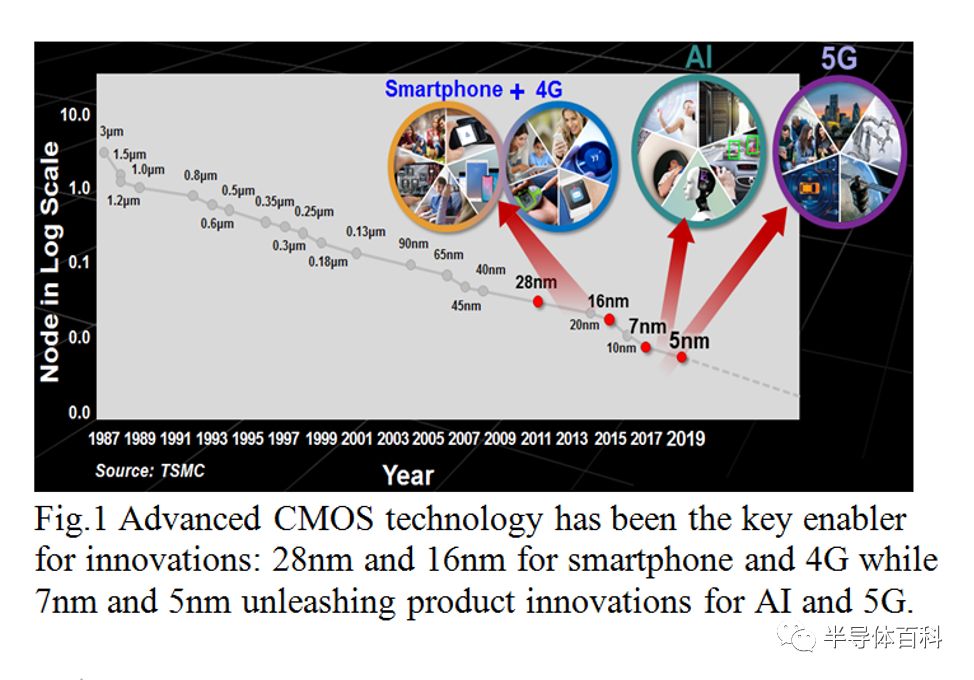

图1表达出一个明确的信息,台积电的5nm瞄准的是AI和5G这两大热门。

图2所展示的信息之前有被报道过,同功率下速度提升15%,或者同速度下有30%的功耗降低,此外逻辑密度是7nm的1.84倍。令人惊奇的是会提供7个Vt,所以7个Vt的调法应该很有意思。随着gate length减小,gate的film stack依靠厚度调节Vt的空间越来越小,界面偶极子的引入是必然,当然这也会让其tuning手法更显神秘。

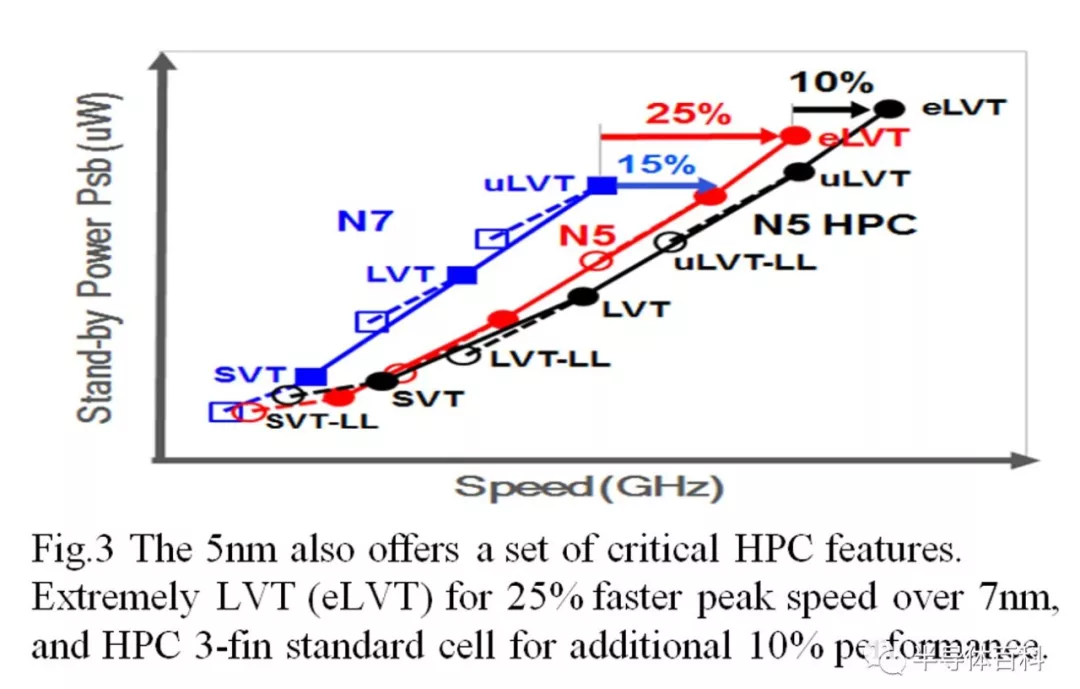

图3是之前没有展现出来的,不过文字里面提到了。eLVT提供了额外的10%的性能提升。此外这里写的是HPC3-fin提供了在额外的10%性能提升,据James的文章,其主要归功于Via Piller 和后段金属工艺的优化,所以整体提升了35%。关于这里的后段金属工艺优化,可能跟后面提到的石墨烯cap有关。

图4材料中没有呈现出来。

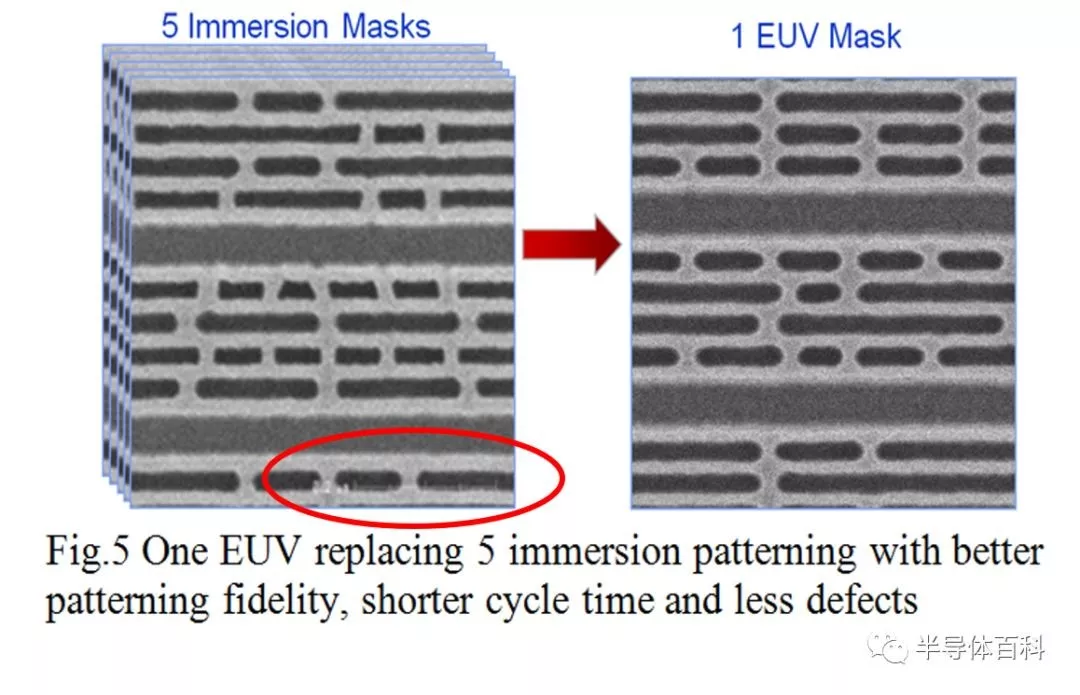

图5之前就有披露,不过James解释的比较粗糙,只是大概量了一下。结合之前Scotten的预测,5nm的标准单元应该还是6T。而此处展示的图应该不是5nm节点的。证据是(图中红圈):左图的右下方还残留着刻度尺,大概可以看到是0.2um,量测下来,左图的标准单元高度大概 245nm。目测是台积电的7nm 6T标准单元的M1层。文中所说5张193i光罩也暗示了其工艺为SALELE,金属节距大概在40nm左右。这也解释了,为什么可以一张EUV光罩可以搞定。

当然这里也体现了台积电的EUV工艺能力,因为之前有一些文章表示,EUV的T2T最多只能做到30nm(好像是三星披露的),这是达不到目前设计的要求的。上图中EUV T2T已经做到跟靠Cut做出来的T2T相当了。所以在真正5nm时其只需要两张EUV光罩做LELE或者SALELE即可,摒弃Cut工艺。从EPE的control方面看SALELE有其天然优势,从成本和through put方面LELE更占优势。当然很遗憾,右边的EUV图没有刻度,所以不清楚其对应尺寸是多少,当然也很难判断是7nm的EUV改进版还是5nm版。笔者认为,如果1张EUV替换5张193i光罩是完全对应的图片的话,右图比较高的可能性是7nm的EUV改进版。所以文献中没有展示其5nm的后段金属工艺。

图6展现了其高迁移率沟道器件的Id-Vg关系图,这些图都是每年的例行公事。

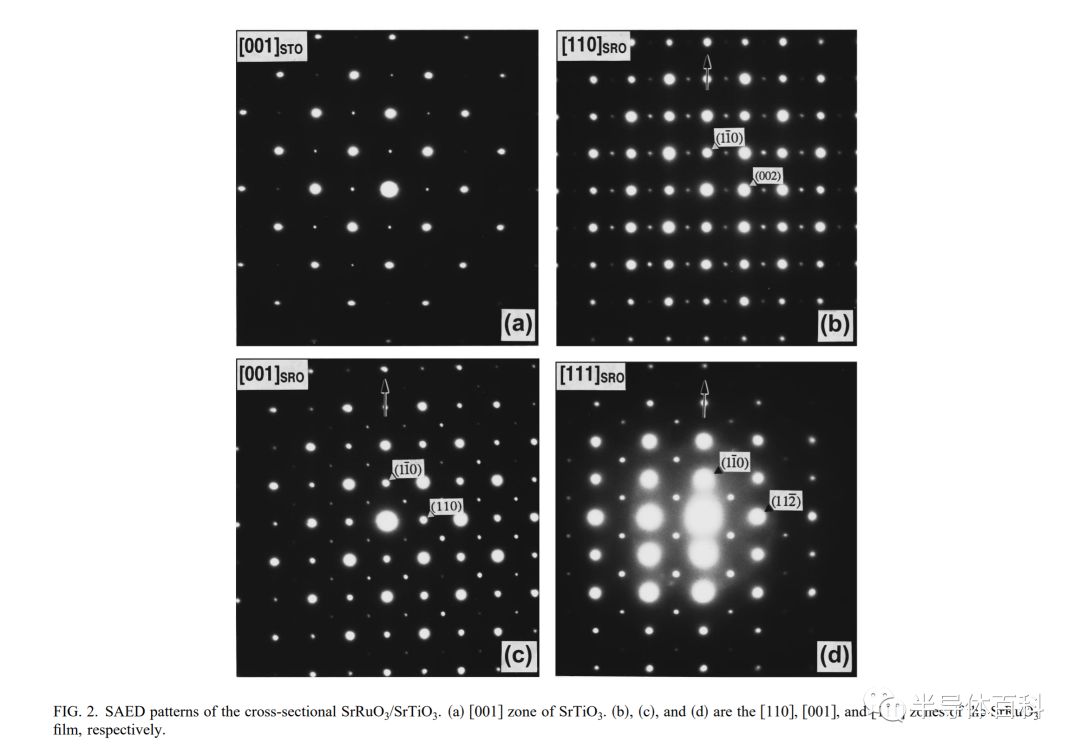

图7在之前的文章中有呈现,18%的性能提升确实非常不错。James 提到的左图TEM和右图的衍射图不匹配。为了验证这个说法搜索了一下,找到一张SrRuO3(好像也是金刚石结构)不同晶向的衍射图[1],对照上去看,确实右侧的衍射图为<100>晶向的,所以这确实是比较疑惑的地方,当然也许这个猜测是错误的,望TEM专家能帮助解惑。

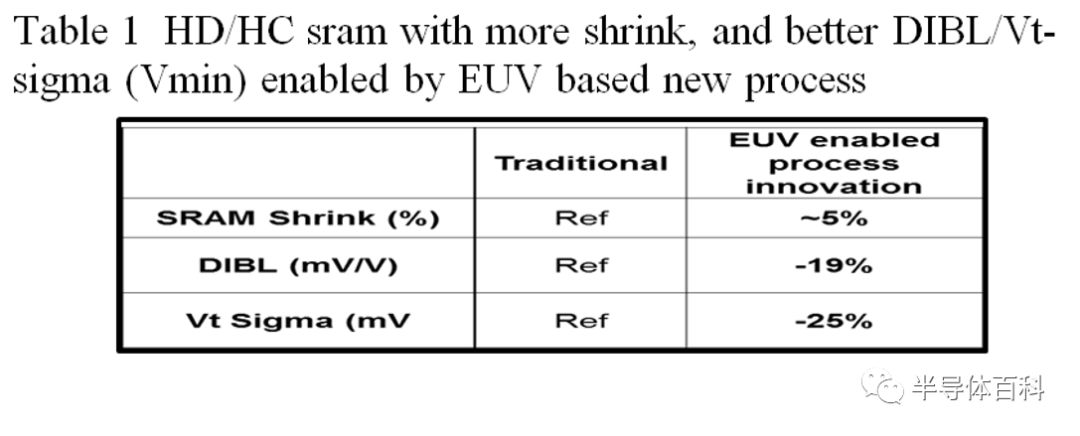

此外还有一张表格1,主要讲的是EUV工艺带来的电性上的提升,我猜测这个提升应该跟图5是对应的,也就是可能这个表格的数据是7nm193i版和EUV版的性能比较。

图8材料中没有呈现出来。

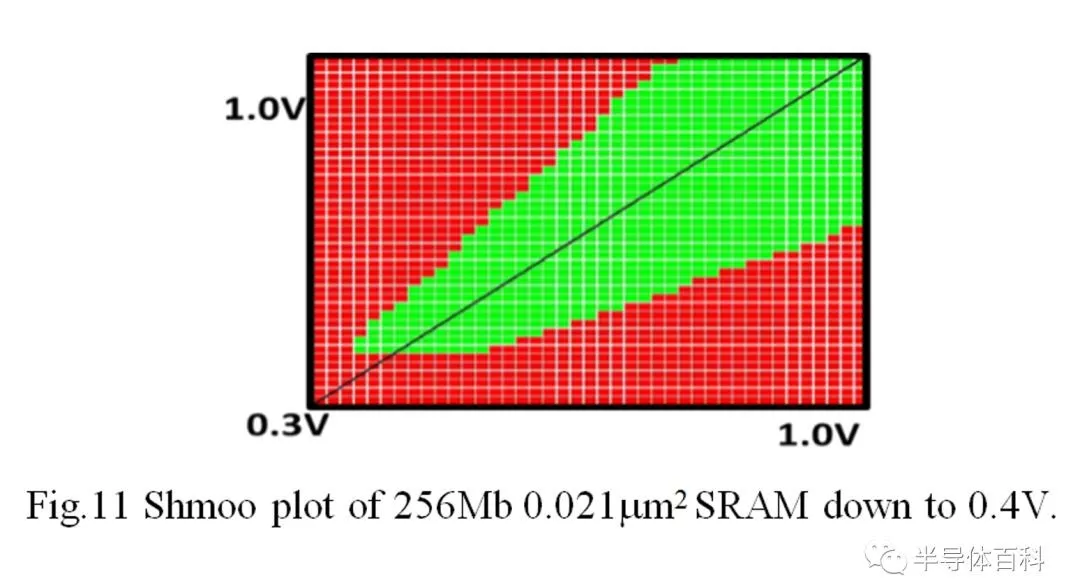

图9在之前的文章中有呈现,0.021um2 的SRAM确实是当今最小的,去年IEDM披露的其7nm SRAM面积是0.027um2。其CPP为57nm,fin pitch为30nm。HDSRAM 16F2算出来是0.02736 um2,比较符合0.027um2的数值,今年如果拿50nm的CPP和27nm Fin Pitch来算,得出的面积是0.0216um2,好像四舍五入不应该是0.021um2。所以这里其SRAM的版图在EUV引入之后有特殊优化,就如表格1中所示可以再缩小5%。当然也有可能跟epi工艺有关,fully guided Epi 可能可以帮助减小两根PMOSfin之间的间距。

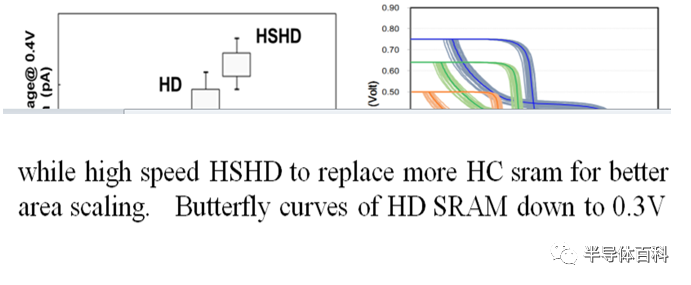

图10在材料中没有完整呈现出来,但是有两片不完整的碎片。里面提到会一个HSHD的SRAM替代HC SRAM,到时候拭目以待。

图11和图12展现其良率已经非常高了,与图6一个性质,例行公事,展示一下牛逼的数据。

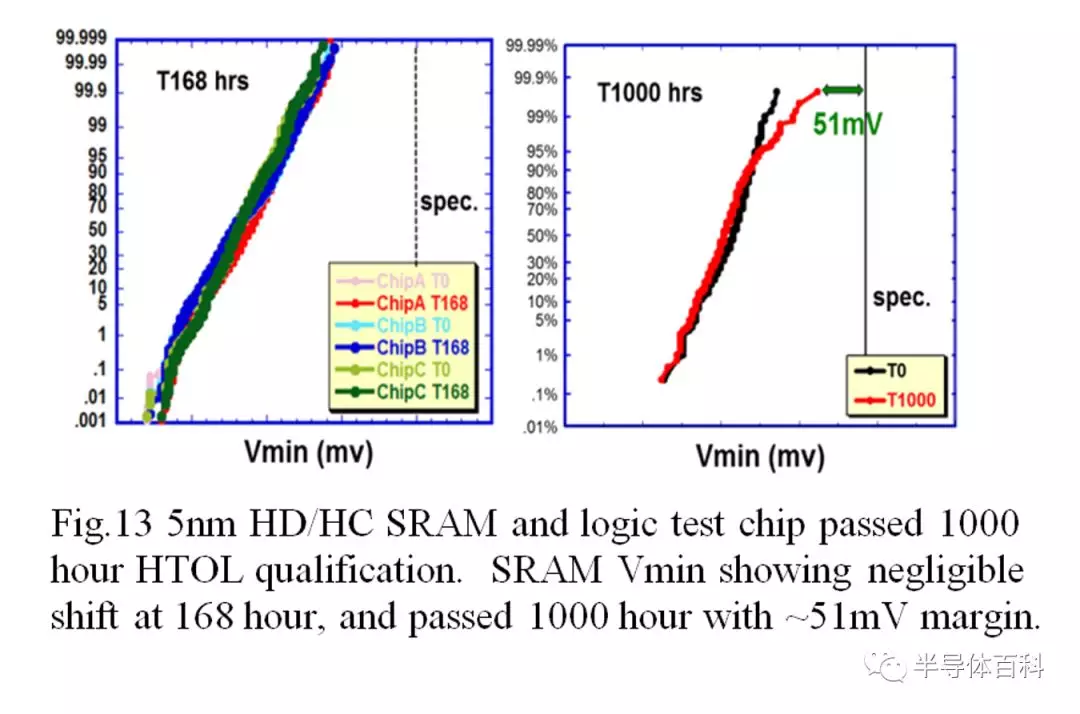

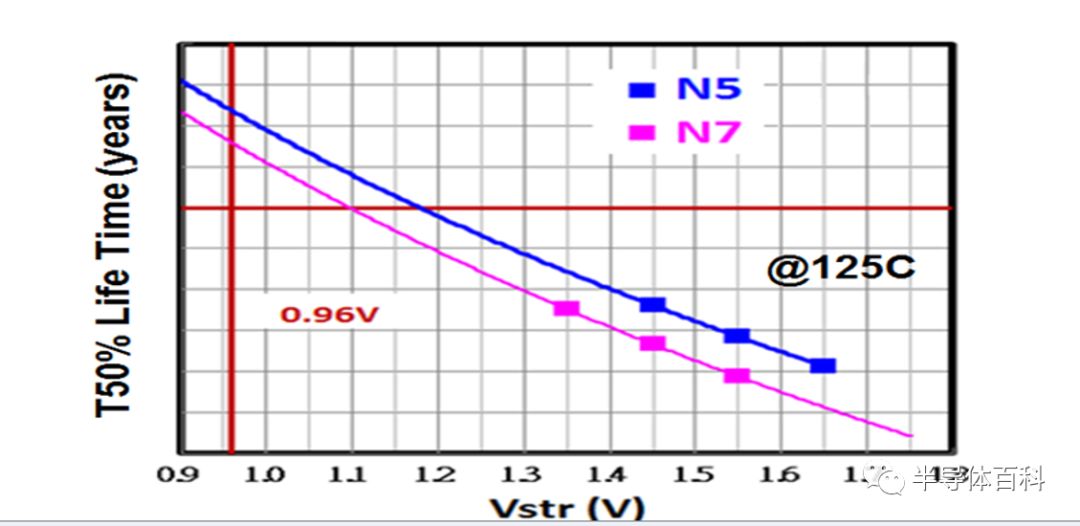

图13展现其器件可靠性。

图14只有一张图没有解释,可能跟其新型low K介电材料的可靠性相关。

图15 就是James 提到的超高密度MIM,其介电材料材质可能和Ti和Sr这两个元素有关。2018年IEDM,IMEC展示了其介电常数高达118的SrTiO3 base DRAM的电容电介质层[2]。可能接下来,也往栅极High-K层里引入,Ti或者Sr是一个趋势。

图16讲的是跟通信相关的,有兴趣的朋友可以看这个:高速Serdes技术的发展趋势和挑战(上)。文中提到IBM在ISSCC 2019会议上发表的单通道128 Gbit/s 1.3 pJ/b的发送器和100 Gbit/s 1.1 pJ/b的接收器,基本代表了当前国际Serdes技术的最高水平,当然这个是基于14nm的。这里5nm可以做到130G/s 0.96pJ/b,也展示了其工艺能力。

当然James提到的低电阻Contact和Via,以及金属等离子体蚀刻,和石墨烯cap并没有在文中提到,应该是他在之前的会议和别的地方听说的。

金属的等离子体蚀刻之前IMEC在推销其BPR时有提及Ru的回蚀刻工艺,和半大马士革工艺里也需要金属蚀刻工艺,所以这可能是一个趋势。至于被蚀刻的材料,应该是Cu的可能性比较低。

石墨烯黏附到金属表面来提升性能之前IEDM有文章报导过,具体查了一下,发现是斯坦福黄汉森教授的团队与Lam和浙大合作做的研究[3]。现在黄汉森加入台积电,可能尝试将相关研究成果引入产线。

总的来说,台积电的工艺研发进度很快,尤其是对EUV工艺的掌握,当然也有一些新的技术尝试,让我们一起期待12月份的IEDM。

本文源自 ,转载目的在于传递更多信息,版权归原作者所有。

参考文献:

[1] 1997 Appl. Phys. Lett. J. C. Jiang et al. “Microstructure ofepitaxial SrRuO3 thin films on (001) SrTiO3”

[2] 2018 IEDM, M. Popovici et al. “High-performance(EOT<0.4nm, Jg∼10−7 A/cm2)ALD-deposited Ru\SrTiO3 stack for next generations DRAM pillar capacitor”

[3] 2016 IEDM, Ling Li et al. “BEOL compatible graphene/Cuwith improved electromigration lifetime for future interconnects”